|

32-разрядные микроконтроллеры семейства FR фирмы Fujitsu

Разрабатывая 32-разрядные микроконтроллеры семейства FR, специалисты фирмы Fujitsu поставили перед собой цель – создать высокопроизводительные 32-разрядные приборы со встроенной периферией, используемой в семействе 16LX . По их мнению, это должно упростить освоение разработчиками систем 32-разрядных микроконтроллеров, способствовать быстрому переводу уже существующих применений на более производительную элементную базу.

Предлагая Вам статью о 32-разрядных микроконтроллерах семейства FR ( Fujitsu RISC ) фирмы Fujitsu , напомню, что в данном журнале был опубликован ряд статей, посвященных 16- разрядным микроконтроллерам семейства 16LX. Напоминание связано с тем, что в этих статьях описаны возможности встроенной 16-разрядной периферии, используемой в микроконтроллерах семейства FR.

В данной статье рассматриваются оснащенные Flash памятью микроконтроллеры, как приборы в наибольшей мере соответствующие потребностям наших сегодняшних разработчиков. Хотя все изложенное в большой степени относится как к микроконтроллерам без памяти программ, так и к программируемым маской приборам.

Семейство FR изначально разрабатывается с ориентацией на требования перспективных применений. В основу этих микроконтроллеров положены разрабатываемые фирмой ядра 32-разрядных RISC процессоров с архитектурой, оптимизированной под встраиваемые применения. При этом разработчики ориентируются на два, в основном, главных требования современного рынка, выдвигаемые автомобильными, потребительскими и коммуникационными применениями - высокая производительность и низкая стоимость.

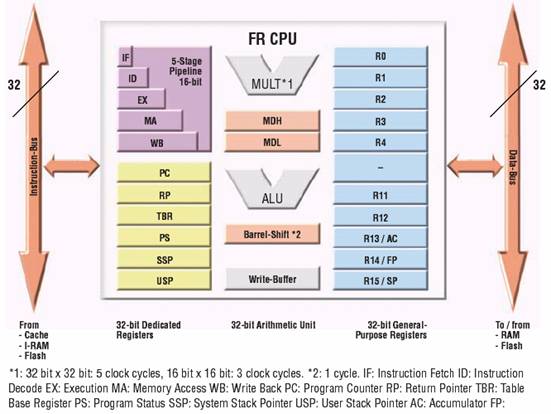

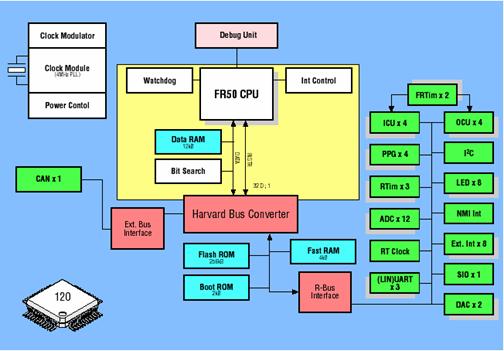

За время, прошедшее с момента выпуска первых микроконтроллеров семейства FR , было разработано и активно используется несколько версий программно совместимых ядер. Первые FR микроконтроллеры серий MB911xx были построены на ядре FR30, на ядре FR50 построены микроконтроллеры серии MB 9136x , внедряются и разрабатываются новые версии ядер в наибольшей мере ориентированных на требования тех или иных применений. И все эти ядра остаются программно совместимыми. Фирма не стремится раскрывать секреты своей интеллектуальной собственности, однако основные, присущие практически всем версиям, характеристики ядер семейства FR мы проиллюстрируем блок-схемой, показанной на Рис. 1, и перечислением основных особенностей ядра.

Рис. 1. Блок-схема ядра CPU семейства FR

Основные особенности ядра семейства FR :

- 32-разрядная RISC архитектура загрузки/сохранения

- Максимальная производительность: 1,25 команды за один цикл сигнала тактирования

- 5-уровневый конвейер 16-разрядных команд

- Встроенный, поддерживаемый на уровне команд, перемножитель,

- 32-разрядное перемножение со знаком за 5 циклов

- 16-разрядное перемножение со знаком за 3 цикла

- Восемь 32-разрядных специальных регистров:

- счетчик команд ( PC ),

- указатель возврата ( RP ),

- регистр базовой таблицы ( TBR ),

- регистр состояния программы ( PS ),

- указатель системного стека ( SSP ),

- указатель стека пользователя ( USP ),

- регистры MDH и MDL (используются перемножителем для сохранения результатов 32- и 16-разрядного перемножения/деления )

- Банк из шестнадцати 32-разрядных регистров общего назначения ( R0 ~ R15). Функции регистров с R 13 по R 15 зарезервированы за виртуальным аккумулятором, указателем фреймов и указателем стека, соответственно

- Набор оптимизированных под встраиваемые применения базовых 16-разрядных команд фиксированных форматов, выполняемых за один цикл; команды пересылок память/память, команды манипулирования битами, команды, ориентированные на языки высокого уровня. В системе команд имеются также команды и 32- и 48-разрядного формата

- Быстрый отклик на прерывания (6 циклов), поддержка вложенных прерываний, 16 уровней приоритета с маскированием

- Линейное адресуемое пространство в 4 Гбайта

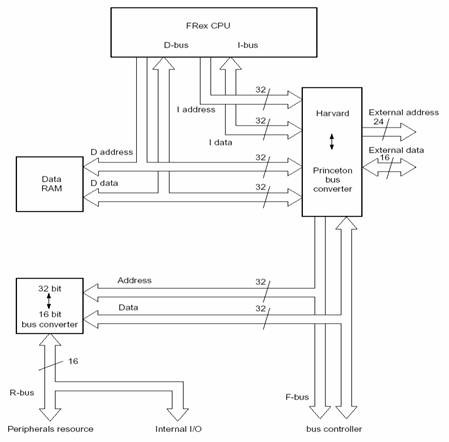

Архитектура шин микроконтроллеров семейства FR ориентирована на использование встроенной периферии 16-разрядных микроконтроллеров семейства F2MC-16LX и 16-разрядных команд фиксированного формата, необходимых для такой интеграции. Типовая схема организации шин микроконтроллеров семейства FR показана на Рис. 2.

Рис. 2. Пример архитектуры шин микроконтроллеров семейства FR

Блоки, которым необходим быстрый доступ, соединены с FR-ядром 32-разрядной Гарвардской шиной (раздельные 32-разрядные шины команд I - bus и данных D - bus ). Такими блоками могут быть: встроенная сверхоперативная RAM и кэш (если они используются), контроллер DMA и модуль поиска битов 1). К шинам I - bus и D - bus подключен и преобразователь шин Гарвард/Принстон, организующий 32-разрядную шину F - bus , используемую для обеспечения доступа к встроенной Flash памяти, к контроллерам CAN и другим ресурсам, интенсивно обменивающимся данными с ядром. Интерфейс внешней шины, как правило, организуется преобразователем шин Гарвард/Принстон, оптимизирующим порядок обращения к внешней шине. Встроенные буферы записи и предварительной выборки исключают потребность в ожидании шины CPU .

Ресурсы, которым достаточно простого управления или управления доступом по состоянию, типа UART, таймеров и т.д., подключаются к 16 разрядной шине периферии R- b us. Преобразователь 32-разрядного формата в 16-разрядный формат R-шины, представляющий собой блок преобразования, подобный блоку интерфейса внешней шины, принимает 32-разрядные обращения CPU к периферии и преобразует их в два 16-разрядных обращения, обеспечивая взаимодействие 16-разрядной встроенной периферии с 32-разрядным CPU .

Бросается в глаза большое сходство архитектуры FR с архитектурой 32-разрядных микроконтроллеров других фирм, например Atmel , использовавших 16/32-разрядное лицензионное ядро ARM7TDMI , однако ядро FR фирма Fujitsu разработала самостоятельно .

Модуль поиска битов используется микроконтроллером при работе с встроенными операционными системами и позволяет за один машинный цикл обнаружить в 32-разрядном слове бит первым, начиная с MSB , изменившим свое состояние. Результатом детектирования является положение этого бита.

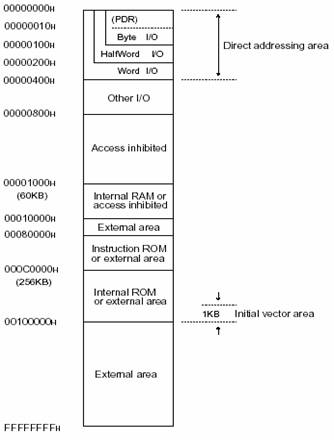

На Рис. 3 приведена типовая карта памяти приборов семейства FR (в зависимости от конкретного типа прибора она может иметь несколько иной вид).

Рис. 3. Карта памяти микроконтроллеров семейства FR в общем случае

Область адресов с 8000 h по C 000 h предназначена для обращения к памяти программ, которая может быть как встроенной, например Flash памятью, так и внешней, обращение к которой ведется через интерфейс внешней шины.

Flash память микроконтроллеров семейства FR ведет происхождение от приборов памяти типа MBM29LV 40°C. И характеристики и особенности памяти, за малым исключением, например разбиением на секторы, практически идентичны. Так при программировании используется алгоритм автоматического программирования ( Embedded Algorithm ), набор команд работы с памятью совместим с JEDEC стандартом, может быть выполнено стирание как отдельного сектора, так любого сочетания секторов и т.д. Интерфейс Flash памяти обеспечивает запись/стирание как под управлением CPU ( CPU mode ), так и под управлением по внешним выводам ( flash memory mode ). Встроенная Flash память микроконтроллеров семейства FR обеспечивает, как и ее прародитель, минимум 10000 циклов стирания/записи и сохранность данных не менее 10 лет.

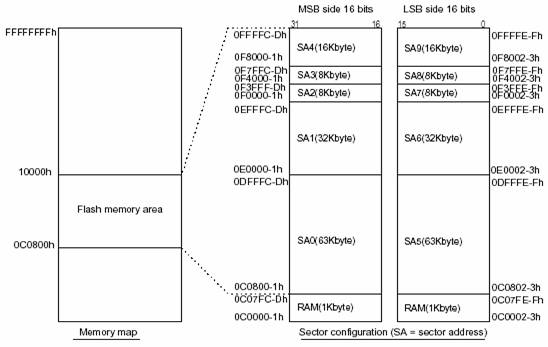

Отметим разбиение встроенной Flash памяти на набор секторов (в зависимости от емкости встроенной Flash памяти и количество секторов и их емкость могут варьироваться), обеспечивающее чтение/запись 16-разрядных полуслов и чтение байтов и 32-разрядных слов. Пример секторной организации Flash памяти приведен на Рис. 4.

Рис. 4. Пример секторной организации Flash памяти емкостью 254 кбайта

Заодно отметим, что размещение битов 32-разрядного слова данных соответствует порядку little endian ( LSB соответствует биту 0), а размещение байтов соответствует порядку big endian (байт 0 размещается по адресу « n », байт 1 размещается по адресу « n + 1», байт 2 размещается по адресу « n + 2» и т.д.).

Flash микроконтроллеры серии MB91F36xG (к этой серии относится и прибор MB91F37 GA ) оснащены ROM загрузки. В этой ROM , с которой начинается работа микроконтроллера после сброса или инициирования, хранятся подпрограммы последовательного программирования встроенной Flash памяти и конфигурирования микроконтроллера.

Самое время коснуться интерфейса внешней шины, обеспечивающего обращение, как к внешней памяти, так и внешним устройствам I / O . Основные возможности интерфейса внешней шины микроконтроллеров семейства FR следующие:

- Вывод адреса форматом до 25 разрядов (зависит от типа прибора)

- Выбор, заданием сигнала CS , одного из нескольких банков внешнего адресуемого пространства (минимальный объем банка 64 кбайта)

- Задание для выбранного сигналом CS банка 8-, 16- или 32-разрядного формата данных (набор форматов зависит от типа прибора)

- Программное задание времени ожидания памяти (до 7 циклов)

- « Fly - by » поддержка контроллером DMA

- Поддержка DRAM ( MB91F109)

- Работа с частотой тактирования, в большинстве случаев, 25 МГц

Отметим наличие у прибора MB91F312, вместо привычного интерфейса внешней шины, обслуживающего обычно внешнюю память и внешние периферийные устройства, 16-разрядного интерфейса входа/выхода, обслуживающего только макрофункции USB, MS-IF и OSDC и работающего с максимальной частотой 20 МГц.

Встроенная периферия, как уже отмечалось, это 16-разрядная периферия, аналогичная используемой в 16-разрядных микроконтроллерах фирмы Fujitsu . Примером насыщения микроконтроллера семейства FR встроенной периферией может служить блок-схема микроконтроллера типа MB91364G (См. Рис. 5). Приборы серии MB91F36x с встроенной Flash памятью и интерфейсами CAN предназначены для использования в самых различных автомобильных и промышленных применениях. Так сегодня они используются в высокопроизводительных измерительных системах, которым необходима специальная встроенная периферия, типа контроллеров шаговых двигателей, таймеров реального времени, генераторов звукового сигнала, драйверов LED и PPG для управления интенсивностью свечения.

Рис. 5. Блок-схема микроконтроллера MB91364G

Описание стандартных модулей периферии, таких как таймеры/счетчики, ADC и DAC , часы реального времени и т.п., и их работа представлены в упомянутом выше «Справочном руководстве». Основным отличием модулей можно считать то, что модули 16-разрядных микроконтроллеров располагают собственными регистрами переключения функций выводов, тогда как в приборах семейства FR переключение функций выводов организуется специальными регистрами переключения функций I / O . Кроме того, разрешение ADC и DAC увеличено до 10 разрядов.

Структуры модулей интерфейсов микроконтроллеров семейства FX и семейства 16 LX практически полностью идентичны, но отмеченные у стандартной периферии отличия, такие как управление I / O , касаются и модулей интерфейсов. Необходимо отметить, что в приборах семейства FR модули интерфейсов с интенсивным обменом данных ( CAN , USB ) подключаются к 32-разрядной Принстонской шине ( F - bus ), как и встроенные RAM и Flash память. Кроме того, в приборах семейства FR бодовая скорость модулей UART , в том числе и с LIN -функциональностью, организуется специальными закрепленными за каждым модулем UART 16-разрядными таймерами ( U - Timer ).

Практически идентичны архитектуры контроллеров шаговых двигателей. Основное усовершенствование – введение детектора нулевого положения ротора и соответствующего регистра управления.

Как и все современные микроконтроллеры, приборы семейства FR оснащены средствами восстановления работоспособности системы (сброс по сторожевому таймеру, внешний сброс, сброс по подаче питания и т.п.). Ряд микроконтроллеров оснащен компараторами уровня – схемами обнаружения недо/перенапряжения питания ( alarm comparator ). Используются два режима энергосбережения ( Stop и Sleep ) и, кроме того, режим Gear – режим, в котором CPU и периферия работают с отличающимися в целое число раз частотами тактирования, что способствует оптимизации работы микроконтроллера в целом и потребления в частности.

При разработке современных микроконтроллеров особое внимание уделяется электромагнитной совместимости, что связывается с исключительно плотным размещением компонентов на печатных платах минимальных размеров и, следовательно, сильным взаимовлиянием компонентов. Снижению уровня электромагнитного излучения способствует оснащение микроконтроллеров семейства FR тактовыми генераторами, работающими с недорогими кварцами невысокой частоты. Так тактовый генератор серии MB 91 F 36 x работает с кварцем на 4 МГц. При этом, встроенная схема PLL доводит частоту сигнала тактирования CPU до частоты в 64 МГц. Кроме того, ряд микроконтроллеров оснащен и тактовыми генераторами, работающими с резонаторами на частоту 32,768 кГц (аналогично субтактированию микроконтроллеров семейства 16 LX ) в том числе со схемой калибровки часов реального времени по кварцу с частотой 4 МГц. Еще одним средством снижения EMI является модуляция сигнала тактирования. Суть этого приема заключается в том, что при незначительном изменении частоты тактирования (например, от 39,6 до 40,4 МГц, при центральной частоте 40,0 МГц) энергия излучения на частоте 40 МГц «размазывается» по диапазону частот и пик мощности излучения при этом существенно снижается. Напомним, что первыми микроконтроллерами фирмы Fujitsu , оснащенными блоком модуляции стали 16-разрядные микроконтроллеры серии MB90F390, модули которых описывались в «Справочном руководстве».

Наличие ядра собственной разработки (не приобретенного по лицензии, как, например, ARM7TDMI ) позволило фирме Fujitsu вести работу по совершенствованию ядер семейства.

Последними, добавленными к номенклатуре семейства FR , приборами стали микроконтроллеры серий MB913x , MB9135x и MB912xx (см.  Табл. 1 394Кб) и в основу приборов первых двух серий положено уже ядро FR 60, в котором, по утверждению специалистов фирмы, были проведены работы по оптимизации работы внутренних шин. Обратите внимание - микроконтроллер MB 91 F 312 оснащен модулем контроллера символов TV дисплея – модулем, который не встречался ни в семействе 16 LX , ни в других приборах семейства FR . Основной задачей этого модуля является формирование символов (в первую очередь символов разнообразных меню) которые необходимо выводить на экран TV приемника, игровой приставки и т.п. Возможность использования этого микроконтроллера в различной аппаратуре расширены наличием хоста и устройства USB . Табл. 1 394Кб) и в основу приборов первых двух серий положено уже ядро FR 60, в котором, по утверждению специалистов фирмы, были проведены работы по оптимизации работы внутренних шин. Обратите внимание - микроконтроллер MB 91 F 312 оснащен модулем контроллера символов TV дисплея – модулем, который не встречался ни в семействе 16 LX , ни в других приборах семейства FR . Основной задачей этого модуля является формирование символов (в первую очередь символов разнообразных меню) которые необходимо выводить на экран TV приемника, игровой приставки и т.п. Возможность использования этого микроконтроллера в различной аппаратуре расширены наличием хоста и устройства USB .

Однако существенно больший уровень доработок был выполнен на ядре микроконтроллеров серии MB912xx – микроконтроллеров, в основу которых положено оптимизированное под нужды снижения размеров кристалла (следовательно, снижения стоимости приборов) и снижения потребления ядро FRLite (в ряде материалов фирмы это ядро обозначается как FR60Lite ). Результатом оптимизации архитектуры стало прямое подключение Flash памяти к I -шине, результатом оптимизации распределения сигналов тактирования стало снижение потребления. Предлагая заказчикам микроконтроллеры серии FRLite , специалисты фирмы утверждают что:

- это ядро позволило закрыть промежуток производительность/стоимость между сегодняшними 16LX и FR контроллерами

- производительность микроконтроллеров на ядре FRLite в пять раз выше, чем у приборов 16LX (20 MIPS при частоте 32 МГц) но потребление энергии (1 мА/МГц, что на 40% меньше, чем у типовых 32-разрядных RISC ядер) и уровень EMI остались такими же, что у 16-разрядных CPU

- это ядро еще более упрощает переход из CISC мира 16LX в 32-разрядное RISC пространство семейства FR

- стоимость 32-разрядных приборов серии MB91F2xx очень близка к стоимости 16-разрядных приборов семейства F2MC-16LX

Несмотря на все доработки ядер, микроконтроллеры семейства FR остаются программно совместимыми, и для разработки систем на их основе используется одно и то же средство разработки - Softune Workbench - интегрированный пакет, работающий в среде операционных систем Windows 95/98, Windows NT4.0, Windows 2000 и Windows XP.

В стандартный пакет входят:

- ANSI C Compiler

- Macro Assembler

- Linker

- Simulator

- Emulator

- C Checker

- C Analyser

Интерфейс пользователя Softune Workbench обеспечивает свободный доступ ко всем средствам разработки с большим количеством возможностей, позволяющих разработчику сконцентрировать свое внимание на разработке кода и процессе отладки, не задумываясь о том, как запустить компилятор или линкер и т.д.

Теперь заглянем немного вперед.

Что же предложит разработчикам фирма Fujitsu в ближайшей перспективе?

В конце октября 2003 года фирма Fujitsu сообщила о проведении работ по созданию ядра FR80, самого мощного 32-разрядного RISC ядра микроконтроллеров семейства FR. Побудительным мотивом к разработке нового ядра стало введение в Японии цифрового вещания которое, как ожидается, поднимет спрос на цифровое TV , на средства DVD и HDD записи. Следовательно, возникнет потребность в высокопроизводительном CPU с необходимой для таких устройств производительностью.

Ядро FR80 будет изготавливаться по технологии с топологическими нормами 0,18 мкм (напомню, что для ядра FR 60 использовались топологические нормы 0,35 мкм), что позволит ядру работать с частотой тактирования до 200 МГц, что более чем в два раза выше, чем у ранее разработанных приборов семейства FR. При частоте тактирования 200 МГц, процессор FR80 будет обеспечивать производительность в 259 MIPS, потребляя всего 140 мА тока (0,54 мА/MIPS), что является одним из лучших соотношений для 32-разрядных RISC процессоров, изготавливаемых по технологии 0,18 мкм. Кроме того, FR80 остается совместимым с системой команд семейства FR, позволяя потребителям, уже использующим приборы семейства FR, модернизировать свои разработки без замены уже разработанных программных ресурсов.

Как и для ранее выпускавшихся приборов семейства FR, разработка программных средств для приборов на основе ядра FR80 будет проводиться на основе пакета Softune Workbench.

Подведем итоги

В семейство микроконтроллеров FR входят приборы нового поколения, располагающие великолепной производительностью RISC архитектуры и встроенными функциями 16-разрядной технологии.

Семейство FR разработано специально под встраиваемые применения с ориентацией на следующие требования:

- расширение возможностей обработки данных;

- введение в RISC систему команд тех команд, которые необходимы для встраиваемых применений;

- обеспечение высокой эффективности объектного кода, и

- насыщенность периферийными функциями

Оптимизацией приборов семейства FR под встраиваемые применения фирма Fujitsu устранила ряд проблем, возникающих перед разработчиком, при переходе от 8- и 16-разрядных к 32-разрядным RISC микроконтроллерам (такие проблемы как: отличающаяся встроенная периферия, иная система команд и увеличенный размер кода).

Евгений Крылов

|