|

Программируемые системные приборы фирмы STMicroelectronics. Часть 3.

8-разрядные микроконтроллеры семейства mPSD3xxx

В данной статье рассматриваются особенности архитектуры 8-разрядных микроконтроллеров семейства mPSD3xxx фирмы STMicroelectronics. Особенностью этих микроконтроллеров является объединение стандартного микроконтроллера с архитектурой 8051 с PSD прибором, что позволило создать ряд серий 8-разрядных микроконтроллеров с исключительно высокими характеристиками.

Восьмиразрядные микроконтроллеры семейства mPSD3xxx, или «Программируемые системные Flash приборы с ядром микроконтроллера 8032 (Flash Programmable System Devices with 8032 Microcontroller Core)», как они называются в фирменных описаниях, получили все достоинства PSD приборов, в том числе внутрисхемное программирование (ISP) посредством JTAG ISP интерфейса и, кроме того, существенно расширенный набор встроенной периферии.

Естественен вопрос: – Почему в приборах семейства mPSD3xxx используется ядро с архитектурой 8051?

Единственного ответа нет и, среди множества ответов, будут:

- Это ядро все еще наиболее популярно среди 8-разрядных микроконтроллеров

- На рынке, составляющем 4 млрд. штук, микроконтроллеры с архитектурой 8051 составляют 15%

- Мощная поддержка архитектуры 8051 третьими поставщиками

- Колоссальное количество пользователей

- Огромный опыт разработчиков, громадные объемы апробированных программных средств

- Естественное сопротивление разработчиков переходу на новые и непривычные микропроцессорные архитектуры

- Статистика использования приборов PSD, показавшая, что в большинстве случаев они использовались именно с микроконтроллерами с архитектурой 8051, о чем упоминалось в предшествовавшей статье

Может быть задан и другой вопрос: - Чем отличаются микроконтроллеры семейства mPSD3xxx от традиционных микроконтроллеров и в чем их преимущество? Далеко не полный перечень ответов на этот вопрос приведен ниже:

- Большие объемы Flash памяти и RAM, превышающие, как правило, объем памяти микроконтроллеров традиционных архитектур, наличие вторичной памяти обеспечивают:

- использование языков высокого уровня, операционных систем реального времени (RTOS),

- организацию насыщенного интерфейса пользователя,

- реализацию сложных алгоритмов,

- корректировку программы без остановки выполнения основной задачи

- высокую скорость обмена за счет организации в RAM буфера большого объема.

- Возможность управления распределением памяти посредством встроенной PLD декодирования и регистра страниц:

- программируемая логика декодирования позволяет разместить каждый сектор памяти по любому адресу, по любому пространству кодов или данных, по любой странице памяти,

- встроенная PLD декодирования позволяет преодолеть традиционный, для архитектуры 8051, барьер адресуемого пространства в 64 кбайт, налагаемый 16 линиями адреса,

- 8-разрядный регистр страниц, встроенный в PLD декодирования, эквивалентен добавлению еще 8 линий адреса, что позволяет в 256 раз расширить адресуемое пространство.

- Встроенный последовательный JTAG интерфейс обеспечивает внутрисистемное программирование (ISP) без участия ядра процессора, что позволяет:

- программировать систему с уже запаянным на печатную плату микроконтроллером, что исключит влияние температуры пайки на записанную в память информацию

- выполнить программирование полностью пустого прибора за время порядка 10 – 25 секунд.

- Перепрограммирование в условиях эксплуатации (IAP) с использованием практически любого канала связи.

- Встроенная программируемая логика с макроячейками входа и выхода, аналогичная стандартной архитектуре 22V10, исключает использование внешних приборов PAL, PLD и логики 74HC74xx и обеспечивает организацию непосредственно в микроконтроллере:

- необходимой «склеивающей» логики,

- конечных автоматов, сдвиговых регистров, счетчиков, декодеров, мультиплексоров, делителей частоты, генераторов задержки и пр.

- Стековая технология

Как правило, пользователя не интересует, что находится в маленьком корпусе с большим количеством выводов. Тем не менее, отметим, что при стековой технологии кристалл ядра микроконтроллера 8032 сажается поверх кристалла PSD прибора. Такая технология не только позволила специалистам фирмы STMicroelectronics создать микроконтроллеры с исключительно высокими характеристиками, но и обеспечила им возможность очень быстро выпускать новые микроконтроллеры с еще более высокими характеристиками и с новыми наборами встроенной периферии.

Рис. 1

Стековая технология

Преимущества:

- Экономичнее при больших объемах памяти

- Новые приборы выходят на рынок быстрее за счет совмещения различных кристаллов

- Стали промышленным стандартом за счет использования в сотовой телефонии в сотовой телефонии

На Рис. 1 указано, что изготавливаемые по стековой технологии микроконтроллеры стали промышленным стандартом за счет использования в сотовой телефонии. Однако этим области применения микроконтроллеров семейства mPSD3xxx далеко не ограничиваются и они могут быть использованы:

- в периферии торговых терминалов: сканеры штриховых кодов, ридеры чеков/кредитных карт, термопринтеры, банкоматы, контроль подписей,

- в торговых автоматах: пищевыми товарами и напитками, билетами, на автозаправках, в приемниках бумажных денег и монет,

- в средствах обеспечения безопасности и защиты зданий: в средствах кондиционирования, управления доступом, управления освещением, в средствах чтения удостоверений (Badge),

- в карманных средствах измерений: GPS, тестеры, сканеры инвентаризации,

- в средствах сбора данных: оборудование рабочих мест, медицина, бытовые счетчики расхода и потребления

- и в многих, многих других применениях.

В качестве основы, при рассмотрении особенностей архитектуры микроконтроллеров семейства mPSD3xxx, примем микроконтроллеры mPSD325x, отличающиеся, в основном объемом основной Flash памяти, наличием интерфейса USB и корпусами. Основное внимание, при этом, будет уделяться дополнительным к архитектуре 8032 элементам, поскольку основные элементы, например таймеры/счетчики, совместимы с используемыми в архитектуре 8032 .

Отличительные особенности микроконтроллеров mPSD325x:

- Два банка Flash памяти, обеспечивающие чтение из одного банка памяти во время записи в другой и удаленное обновление программных средств – перепрограммирование в условиях эксплуатации (IAP)

- Основная Flash памяти объемом 128 или 256 Кбайт для размещения кодов программ, операционных систем или битовых карт графического интерфейса пользователя. Разделена на восемь секторов одинаковой емкости

- Вторичная Flash память объемом 32 кбайт разделенная на четыре сектора одинаковой емкости.

Исключает необходимость использования внешней EEPROM

- SRAM объемом 32 кбайт, с возможностью батарейной поддержки

- Программируемая PLD декодирования (DPLD) с встроенным регистром страниц, обеспечивающая гибкое распределение адресов всей памяти

- Высокоскоростное тактирование стандартного ядра 8032 (12 тактов на машинный цикл)

- Работа с тактовой частотой 40 МГц при напряжении питания 5 В и 24 МГц при напряжении питания 3,3 В

- 2 UART с взаимно независимыми бодовыми скоростями, три таймера/счетчика и два внешних прерывания

- Интерфейс USB (mPSD3254A-40)

- Поддержка низкоскоростного режима USB 1.1 (1,5 Мбит/с)

- Управление конечной точкой 0 и прерывания по конечным точкам 1 и 2

- Интерфейс I2C, обеспечивающий связь с периферией в режиме как ведущего, так и ведомого

- Пять 8-разрядных каналов широтно-импульсного модулятора (PWM) из них один с программируемым периодом

- Четырехканальный 8-разрядный аналого-цифровой преобразователь (ADC) с опорным напряжением (VREF)

- Автономный канал отображаемых данных (Display Data Channel - DDC)

- Используется с мониторами, проекторами и TV применениями

- Совместим с VESA стандартами DDC1 и DDC2B

- Исключает потребность во внешней DDC PROM

- Шесть портов I/O, обеспечивающих до 50 выводов

- Программируемая вентильная матрица на 3000 вентилей с 16 макроячейками выхода и 24 макроячейками входа

- Супервизорные функции

- Внутрисистемное программирование (ISP) через JTAG интерфейс

- Защита программных средств пользователя

- Технология «нулевого» потребления (Zero-Power)

- Одно напряжение питания: от 4,5 до 5,5 В или от 3,0 до 3,6 В

- Корпус: 52-выводной TQFP или 80-выводной TQFP, обеспечивающий организацию внешней шины

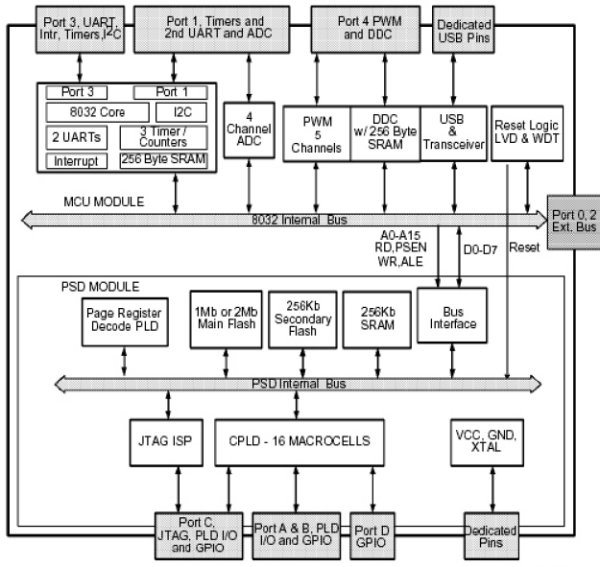

Рис. 2. Блок-схема микроконтроллера mPSD325x

На блок-схеме микроконтроллера mPSD325x, показанной на Рис. 2, видна стековая структура микроконтроллера – кристалл модуля MCU с ядром 8032 (с соответствующей архитектуре 8032 встроенной периферией и портами) и дополнительной периферией, расширяющей возможности микроконтроллера и обеспечивающей поддержку системы, и кристалл модуля PSD идентичного, в основном, прибору, описанному в предшествовавшей статье. В модуле PSD расположена конфигурируемая память программ и данных для ядра 8032 и, кроме того, программируемая логика распределения памяти, программируемая логика общего назначения и программируемых порты A, B, C и D с архитектурой отличной от архитектуры портов 0 – 4 модуля MCU.

Поскольку в основе модуля MCU лежит ядро 8032, то в набор регистров специальных функций входят все SFR регистры архитектуры 8032 (A, B, SP, PC, PSW, DPTR и регистры встроенной в 8032 периферии) и к ним добавлены регистры организации работы новой встроенной в модуль MCU периферии (каналы PWM, ADC, DDC, интерфейсы I2C и USB и другая встроенная периферия). Напомним, как отмечалось в предшествовавшей статье, что регистры управления конфигурацией PLD (распределения памяти, конфигурирования портов и пр.) находятся в пространстве CSIOP – отдельном блоке энергонезависимой памяти объемом 256 байт, размещаемом в пространстве адресов микроконтроллера и обеспечивающем, следовательно, адресацию микроконтроллером всех находящихся в этом пространстве регистров. Первичное конфигурирование этих регистров выполняется средствами проектирования PSDsoft.

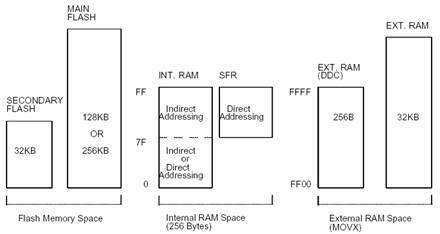

Стандартное ядро архитектуры 8032, используемое в приборах mPSD325X, работает с раздельными пространствами адресов памяти программ и данных объемом по 64 Кбайт. Расположенная в модуле PSD Flash память, которая может быть отображена как в пространстве программ, так и в пространстве данных, состоит из двух блоков: основной (1 или 2 Мбит) и вторичной (256 кбит) Flash памяти. Преодоление ограничения пространства адресов в 64 кбайт организуется 8-разрядным регистром страниц, обеспечивающим 256-кратное расширение адресуемого пространства. За исключением времени выполнения процедур программирования или модификации, Flash память обеспечивает только чтение, но не запись.

Ядро 8032 работает с внутренней и внешней памятью данных обеспечивающей как чтение, так и запись. В объем внутренней SRAM, составляющий 256 байтов, входит область стека.

Старшие 128 байтов внутренней SRAM занимают регистры специальных функций (SFR) и к этим регистрам обращение идет только в режиме прямой адресации.

Прибор mPSD325X располагает еще двумя блоками внешней, относительно ядра 8032, SRAM: один блок емкостью 256 байтов предназначен для хранения данных DDC. Другой блок SRAM емкостью 32 Кбайт, находящийся в модуле PSD, может быть отображен в любом задаваемом пользователем пространстве адресов.

Рис. 3. Карта памяти и пространство адресов

Дополнительными к архитектуре 8032 функциями модуля MCU являются: второй UART, 4-канальный 8-разрядный аналого-цифровой преобразователь (ADC), 5 каналов широтно-импульсного модулятора (PWM), блок супервизорных функций (детектор снижения напряжения питания – LVD и сторожевой таймер – WDT), два канала шины I2C (один канал, совместно со специальным блоком SRAM, емкостью 256 байтов, используется для организации канала отображаемых данных (Display Data Channel – DDC).

Представление о средствах управления встроенной периферией модуля MCU дает карта регистров специальных функций, см. Табл.

Табл. 4. Карта распределения памяти регистров специальных функций (SFR) модуля MCU

Наличие дополнительных функций привело к тому, что в модуле MCU был организован пятый порт I/O – порт 4, выполняющий функции как I/O PWM и DDC, так и I/O общего назначения. Архитектура и основные функции портов с 0 по 3 аналогичны архитектуре и функциям портов стандартных микроконтроллеров 8032 (порт 2 имеет только 4 вывода – с 0 по 3), однако, в связи с добавлением новых периферийных функций, альтернативные функции выводов портов изменились (см. Рис. 2). Управление альтернативными функциями порта 1 организуются регистром P1SFS, за исключением таймера 2 и UART2 разрешение которых организуется их собственными регистрами конфигурации, управление альтернативными функциями порта 3 и порта 4 организуется с использованием регистров выбора специальных функций P3SFS и P4SFS. При сбросе выводы I/O по умолчанию устанавливаются в режим I/O общего назначения. Альтернативная функция разрешается, если соответствующий бит в регистре PxSFS установлен в состояние 1.

Отметим, что у приборов в 52-выводных корпусах порты 0 и 2 модуля MCU отсутствуют, отсутствует и порт A модуля PSD.

В приборах mPSD325X к стандартному для архитектуры 8032 полнодуплексному приемопередатчику (UART) добавлен еще один (UART2) – полностью аналогичный первому. Первый порт соединен с выходами P3.0 (RX) и P3.1 (TX). Второй порт подсоединен к выводам P1.2 (RX) и P1.3 (TX). Работа этих двух последовательных приемопередатчиков и средства управления обычными четырьмя режимами одинакова и управляется регистрами, соответственно, SCON и SCON2.

Модуль MCU приборов mPSD325X оснащен 4-канальным 8-разрядным аналого-цифровым преобразователем (ADC) последовательного приближения. Аналоговое опорное напряжение подается на вывод AVREF. Каналы подключаются к схеме выборки/хранения мультиплексором, управляемым битами ADS0 и ADS1 регистра управления ACON. Результат преобразования сохраняется в регистре ADAT. Частота тактирования логики ADC должна быть порядка 6 МГц и настройка частоты тактирования организуется 8-разрядным предварительным делителем системного тактового сигнала ASCL. По завершению преобразования, отмечаемому установкой бита ADSF регистра ACON, может быть сформирован запрос прерывания INT1.

Отличительными особенностями блока PWM, которым оснащен модуль MCU, являются:

- четырехканальный 8-разрядный PWM модуль (PWM 0 – 3) с предварительным 16-разрядным делителем,

- одноканальный 8-разрядный модуль PWM (PWM 4) с предварительным 16-разрядным делителем и с программируемыми частотой и шириной импульса,

- программируемая полярность PWM выходов.

В четырехканальном модуле PWM 8-разрядный счетчик PWM считает по модулю 256 (то есть, от 0 до 255, включительно). Значение, сохраняемое в 8-разрядном счетчике, сравнивается с содержимым регистра специальных функций (PWM 0-3) соответствующего канала PWM. Полярность выходов PWM программируется и задается битом PWML регистра PWMCON. Если содержимое регистра PWM 0-3 больше значения счетчика, то соответствующий выход PWM, устанавливается на высокий уровень (при PWML = 0). Если содержимое этого регистра меньше или равно значению счетчика, то соответствующий выход PWM устанавливается на низкий уровень (при PWML = 0). Следовательно, соотношение ширины импульса и длительности периода определяется содержимым соответствующего регистра специальных функций PWM (PWM 0-3). Загружая соответствующий регистр специальных функции (PWM 0-3) состоянием 00h или FFh, выход PWM можно постоянно удерживать, соответственно, на высоком или низком уровне (при PWML = 0). Выходной сигнал выводится через выводы 3, 4, 5 и 6 порта 4.

Четырехканальный PWM модуль оснащен 16-разрядным предварительным делителем 0, делящим частоту основного входного тактового сигнала до частоты сигнала PWM модуля и обеспечивающим получение необходимой частоты повторения сигнала четырехканального PWM модуля. Для хранения 16-разрядного значения деления используются SFR регистры PSCL0L и PSCL0H (адреса B1h и B2h).

Частота повторения выхода PWM модуля вычисляется по выражению:

fPWM8 = (fOSC / предделитель0) / (2 x 256)

и входная частота тактирования счетчика PWM = fOSC / 2 / (значение данных предделителя0 + 1)

Программируемый канал PWM 4 позволяет сформировать на выходе PWM 4 (вывод 7 порта 4) сигнал с переменными шириной импульса и периодом. PWM 4 оснащен 16-разрядным предварительным делителем, 8-разрядным счетчиком, регистрами ширины (PWM4W) импульса и периода (PWM4P).

16-разрядный предварительный делитель 1 делит входной тактовый сигнал (fOSC/2) до желаемой частоты, поступающей на 8-разрядный счетчик канала PWM 4.

Входная частота тактирования счетчика PWM 4:

fPWM4 = (fOSC/2) / (значение данных предделителя1 + 1)

При установке в регистре предварительного делителя 1 (PSCL1L и PSCL1H (адреса B4h и B3h)) значений 0, максимальная входная частота счетчика PWM4 равна fOSC/2 и может достигать частоты 20 МГц.

Выход 8-разрядного счетчика свободного счета PWM 4 сравнивается с содержимым регистров сравнения, загружаемыми данными регистров ширины импульса (PWM4W, ABh) и периода (PWM4P, AAh), задающими, соответствено, длительность импульса и период PWM. Если канал PWM 4 разрешен, значения регистров загружаются в регистры компаратора и сравниваются с выходом счетчика. Если содержимое счетчика равно или больше значения регистра ширины импульса, то выход PWM 4 устанавливается на низкий уровень (при PWMP = 0). Если содержимое регистра периода равно счетчику PWM4, то счетчик очищается и выход канала PWM 4 устанавливается в высокое логическое состояние (начало следующего импульса PWM).

Регистр периода не может иметь значение “00”, и его содержимое должно всегда быть больше значения регистра ширины импульса.

Во время активности канала PWM 4 регистр предварительного делителя 1, регистр ширины импульса и регистр периода могут быть модифицированы. Значения этих регистров автоматически загружаются в счетчик предварительного делителя и регистры компаратора при окончании текущего периода PWM 4.

Регистр PWMCON (биты 5 и 6) управляет разрешением/запретом и полярностью канала PWM 4.

Приборы mPSD325X располагают двумя последовательными I2C каналами каждый из которых поддерживает двухпроводную шину I2C, состоящую из линии данных (SDAx) и линии сигнала тактирования (SCLx) и предназначенные для организации:

- последовательного канала DDC протокола - линии SDA1 и SCL1,

- последовательного канала обычного I2C интерфейса - линии SDA2 и SCL2.

Оба канала могут работать на выход по портам (порт 4 выводы 0 и 1 – линии SDA1 и SCL1, порт 3 выводы 6 и 7 – линии SDA2 и SCL2).

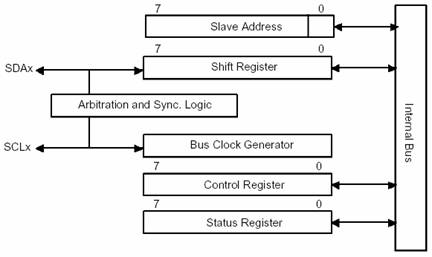

Рис. 4. Блок-схема канала последовательного интерфейса I2C

Система уникальна, поскольку пересылка данных, формирование сигнала синхронизации, распознавание адресов и арбитраж управления шиной - все управляется аппаратными средствами.

Последовательный I/O I2C выполняет полностью автономную обработку байтов и работает в 4 режимах.

- Ведущего передатчика и ведущего приемника,

- Ведомого передатчика и ведомого приемника

Работа в этих четырех режимах организуется следующими регистрами специальных функций (SFR):

- SxCON – управляет обработкой байтов, работой в указанных четырех режимах, в режиме ведущего задает битами CR0~CR2 частоту тактирования,

- SxSTA – значения флагов данного регистра состояния могут быть использованы для запуска различных подпрограмм обслуживания, чем сокращается время ответа программного обеспечения и, следовательно, самой шины I2C,

- SxDAT - регистр сдвига данных, как передаваемых, так и принимаемых. Первым принимается или передается MSB.

- SxADR: регистр адреса ведомого. Распознавание адреса ведомого выполняется встроенными аппаратными средствами.

Кроме того, I2C модуль оснащен регистрами детектирования времени удержания старта/останова и тактирования системы (S1SETUP и S2SETUP), обеспечивающими обнаружения момента старта/останова и возможность работы в широком диапазоне частот тактирования MCU.

Канал отображаемых данных (Display Data Channel - DDC) предназначен для пересылки данных, отображаемых на мониторах, проекторах и в TV применениях. Особенностями канала являются:

- Совместимость с VESA стандартами DDC1 и DDC2B,

- Встроенная SRAM, объемом 256 байтов данных DDC. За загрузку данных DDC в SRAM отвечает ядро 8032,

- Полностью автоматическая работа в режимах DDC1 и DDC2B,

- Работа канала DDC только в режиме ведомого,

- Возможность программного прерывания.

- Детектирование типа головной системы. Процедура детектирования соответствует спецификацией канала данных отображения мониторов VESA (VESA Monitor Display Data Channel - DDC).

Основой модуля DDC являются интерфейс I2C и SRAM хранения данных DDC, что исключает потребность во внешней DDC PROM. Стандартные DDC сигналы интерфейса могут быть направлены к выводам порта 4(VSYNC (P4.2), SDA (P4.0) и SCL (P4.1)).

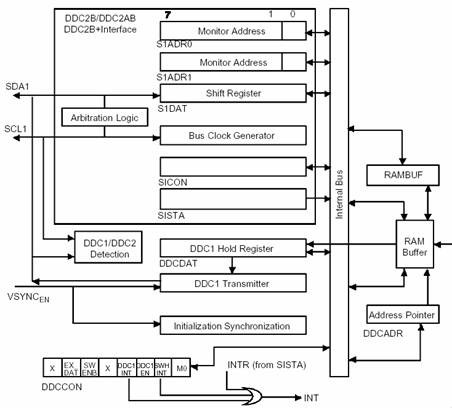

Рис. 5. Блок-схема DDC интерфейса

DDC интерфейс обслуживается восемью регистрами специальных функций (SFR):

- RAMBUF, DDCCON, DDCADR, DDCDAT - регистры собственно DDC.

- S1CON, S1STA, S1DAT, S1ADR - регистры интерфейса I2C, те же самые, что и используемые в шине I2C.

Регистр DDCDAT – 8-разрядный регистр передаваемых в DDC1 протоколе данных, поступающих из буфера RAMBUF. Регистр DDCADR - 8-разрядный регистр указатель адреса с возможностью пост-инкремента. После каждого обращения к регистру RAMBUF (как программными средствами, так и аппаратными средствами DDC1 интерфейса), содержимое этого регистра увеличивается на единицу. Это происходит при работе в обоих протоколах: как в DDC1, так и в DDC2 (DDC2B, DDC2B + и DDC2AB). В регистре управления DDCCON битом Mode задается режим работы (DDC1 или DDC2B), бит SWENB, в зависимости от установленного режима, разрешает прерывание MCU для загрузки следующего байта передаваемых данных, бит DDC_AX определяет адресацию в режиме DDC2B, биты DDC1_Int и DDC1EN определяют работу прерываний в режиме DDC1, бит SWHINT устанавливается аппаратно при переключении DDC из режима DDC1 в режим DDC2b, разрешая прием ожидаемого прерывания. Битом EX_DAT определяется используемый в SRAM объем (128 или 256 байтов).

Протокол DDC1 является интерфейсом точка-точка и при работе в этом протоколе монитор всегда находится в режиме «только передача». Протокол DDC2B разработан на основе интерфейса I2C фирмы Philips. Тем не менее, на уровне DDC2B, головной PC зафиксирован как ведущий, а к монитору всегда обращаются как к ведомому. И ведущий и ведомый могут работать как передатчик или приемник, но задание режима определяет ведущее устройство. В этом протоколе используется указатель адреса.

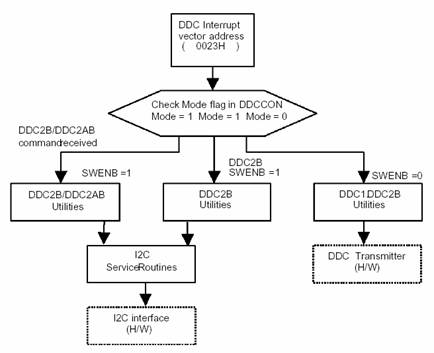

Структура интерфейса DDC показана на Рис. 6.

Рис. 6. Структура интерфейса DDC

Аппаратные средства USB обеспечивают следующие характеристики:

- Соответствуют спецификации USB Rev. 1.1.

- Располагают встроенным SIE (механизм последовательного интерфейса), памятью FIFO и приемопередатчиком.

- Работают на малой скорости (1,5 Мбит/с)

- Поддерживают управление конечной точкой 0 и прерываниями конечных точек 1 и 2

- Частота тактирования USB должна быть 6 МГц (необходимо, чтобы частота тактирования MCU была 12, 24 или 36 МГц).

Внешний аналоговый интерфейс - обычный встроенный приемопередатчик USB. Это сделано с тем, чтобы для интерфейса с физическим уровнем USB можно было использовать уровни напряжения равные VDD стандартной логики.

Блок SIE – цифровой интерфейс (digital-front-end) модуля USB. Этот блок восстанавливает сигнал тактирования 1,5 МГц, детектирует слово синхронизации USB, обрабатывает все USB протоколы низкого уровня и выполняет контроль за ошибками. Схема восстановления тактирования битов восстанавливает тактовый сигнал из входящего потока данных USB и способна отслеживать джиттер и уход частоты согласно USB спецификациям. Кроме того, SIE преобразует электрические сигналы USB в данные или сигналы, в зависимости от адреса устройства USB и оконечной точки USB. В соответствии с адресом, данные USB направляются к адресованной оконечной точке интерфейса SIE. Передаваемые данных от этих аппаратных средств должны быть управляющего типа или прерыванием.

Адрес USB устройства и разрешение оконечных точек программируются в заголовке конфигурации SIE.

Блок USB управляется посредством семи регистров, расположенных в области SFR:

- UADR – регистр адреса USB. Разрешает работу USB и задает адрес USB устройства

- UCON0 и UCON1 – регистры управления оконечными точками USB. Битами регистров разрешаются прием и передача, определяется количество передаваемых данных и пр.

- UCON2 – регистр управления USB. Разрешает и управляет принудительной остановкой оконечных точек 1 и 2.

- UIEN и UISTA – регистры, соответственно, разрешения прерывания и состояния прерывания

- USTA – регистр состояния оконечной точки 0

Кроме указанных регистров управления в работе модуля USB задействованы еще три регистра:

- Регистр передачи данных USB конечной точки 0 (UDT0)

- Регистр приема данных USB конечной точки 0 (UDR0)

- Регистр передачи данных USB конечной точки 1(UDT1)

По адресу E1h расположен 8-разрядный регистр предварительного делителя для USB (USCL). USCL должен быть загружен значением, обеспечивающим частоту тактирования USB в 6 МГц, рассчитываемую по выражению:

Входная частота тактирования USB = (FOSC / 2) / (значение регистра предварительного делителя + 1)

где Fosc - входная частота тактирования MCU.

Примечание: USB работает с частотами тактирования MCU ТОЛЬКО 12, 24 или 36 МГц.

Значения предварительного делителя для этих частот - 0, 1, и 2.

Организация в модуле MCU дополнительной периферии привела к увеличению источников запросов прерываний. В приборах серии mPSD325X теперь их насчитывается 10:

- Внешнее прерывание INT0

- Прерывание по USART 2

- Прерывание по таймеру 0

- Прерывание по I2C

- Внешнее прерывание INT1 (или прерывание по ADC)

- Прерывание по DDC

- Прерывание по таймеру 1

- Прерывание по USB

- Прерывание по USART

- Прерывание по таймеру 2

Общая организация и выполнение прерываний аналогичны прерываниям 8032, в том числе и последовательность опроса при приеме прерываний с одинаковыми уровнями приоритета. Распределение уровней приоритета по периферийным функциям приведено в Табл. 5.

Табл. 5. Уровни приоритета

| Источник |

Уровни приоритета |

| Внешнее прерывание Int0 |

0 (самый высокий) |

| Второй USART |

1 |

| Таймер 0 |

2 |

| Интерфейс I2C |

3 |

| Внешнее прерывание Int1 (прерывание по ADC) |

4 |

| DDC |

5 |

| Таймер 1 |

6 |

| USB |

7 |

| Первый USART |

8 |

| Таймер 2+EXF2 |

9 (самый низкий) |

Итак, мы вкратце рассмотрели «крупные» блоки модуля MCU. Однако, кроме этих блоков в модуле организована и такая «мелочь», как супервизорные функции, отсутствующая в традиционной архитектуре 8032, но без которых не обходится ни один современный микроконтроллер.

В приборах серии mPSD325X реализованы четыре способа организации сброса и инициирования прибора.

- Через вывод входа внешнего сброса

- Встроенным блоком LVR.

- Сигналингом сброса на USB шине.

- Посредством сторожевого таймера

Каждый источник сброса приводит к формированию активного сигнала внутреннего сброса микроконтроллерной системы в начальное состояние. CPU отвечает на этот сигнал выполнением процедуры внутреннего сброса и устанавливает внутренние регистры в определенное состояние. Этот сигнал внутреннего сброса, активный низким уровнем, поступает также на и модуль PSD.

Схема LVR формирует сигнал внутреннего сброса при снижении напряжения питания VDD ниже порога сброса (4 ±0,25 В - при напряжении питания 5 В и 2,5 ±0,2 В - при напряжении питания 3,3 В). Схема LVR обеспечивает гистерезис порядка 0,1 В и задержку подавления шума в 1 мс. После восстановления напряжения VDD до уровня выше порога сброса, сигнал RESET# останется действительным в течение 10 мс, прежде чем будет снят. При начальной подаче питания схема LVR разрешена (по умолчанию), но впоследствии может быть запрещена битом LVREN регистра PCON. Схема LVR продолжает работать и в режиме Idle и в режиме Power-down.

Сторожевой таймер (WDT) состоит из 22-разрядного счетчика, бита сброса по сторожевому таймеру (WDRST) регистра SFR и регистра ключа сторожевого таймера (WDKEY).

Переполнение 22-разрядного счетчика происходит при достижении значения 4194304 (3FFFFFh). Приращение сторожевого таймера происходит с каждым машинным циклом. Таким образом, пользователь должен сбрасывать сторожевой таймер по крайней мере каждые 4194304 машинных цикла (1,258 секунды при 40 МГц). Для сброса сторожевого таймера пользователь должен записать в регистр WDRST значение, находящееся между 00h и 7Eh. Значение, записываемое в WDRST, загружается в 7 старших разрядов 22-разрядного счетчика. Этим пользователю предоставляется возможность достаточно гибко управлять установкой начального значения счетчика, задавая длительность периода срабатывания сторожевого таймера.

Запись в WDRST состояния 00h очищает счетчик. Сторожевой таймер управляется регистром ключа сторожевого таймера WDKEY. Сторожевой таймер блокирует только значение 01010101 (=55h). Остальные сочетания битов оставляют сторожевой таймер разрешенным.

В режиме Idle сторожевой таймер и схема формирования сигнала сброса остаются активными

Модуль PSD приборов серии mPSD325X содержит необходимую для работы ядра 8032 конфигурируемую память программ и данных. Кроме того, модуль PSD располагает собственным набором портов I/O и PLD с набором макроячеек обеспечивающую реализацию логики общего назначения.

Архитектура портов A, B, C, и D - программируемых портов I/O общего назначения, отличается от архитектуры портов I/O модуля MCU.

Модуль PSD связывается с модулем MCU посредством внутренней шины адреса и данных (AO-A15, DO-D7) и сигналов управления (RD#, WR#, PSEN#, ALE, RESET#). Пользователь задает конфигурацию PLD декодирования в пакете разработки PSDsoft и может отображать ресурсы в модуля PSD в любом пространстве адресов программ или данных.

Функциональные возможности модуля PSD

- Flash память емкостью 1 или 2 Мбит. Это основная Flash память, разделенная на восемь блоков одинакового объема к которым можно обращаться по задаваемым пользователем адресам.

- Вторичная (загрузочная) Flash память емкостью 256 кбит. Вторичная память разделена на четыре блока равного объема, к которым можно обращаться по задаваемым пользователем адресам. Вторичная память обеспечивает возможность одновременного выполнения кода и модифицирования основной Flash памяти.

- SRAM емкостью 256 кбит. Содержимое SRAM может быть защищено от потери питания подключением внешней батареи поддержки.

- Комплексная PLD (CPLD) с 16 микроячейками выхода (OMC) и 24 микроячейками входа (IMC). CPLD может использована для эффективной реализации различных логических функций внутреннего и внешнего управления. Примерами такой логики могут быть: конечные автоматы, загружаемые регистры сдвига, загружаемые счетчики, «склеивающая» логика и пр.

- PLD декодирования (DPLD), декодирующая адрес для выбора блоков памяти в модуле PSD.

- Конфигурируемые порты I/O (порты A, B, C и D) которые могут быть использованы для выполнения следующих функций:

- входы - выходы MCU

- входы - выходы PLD

- выходы зафиксированных адресов MCU

- I/O специальных функций.

- порты I/O могут быть конфигурированы как выходы с открытым стоком.

- Встроенный JTAG последовательный порт обеспечивает полное внутрисистемное программирование всего прибора (ISP). Посредством этого порта можно запрограммировать полностью пустой прибор, как в условиях производства, так и в условиях эксплуатации.

- Внутренний регистр страниц, позволяющий расширить адресное пространство модуля MCU 8032 в 256 раз.

- Встроенный программируемый модуль управления питанием (PMU), поддерживающий режим энергосбережения Power-down. PMU может обнаружить отсутствие активных действий ядра 8032 и автоматически перевести модуль PSD в режим Power-down.

- Циклы стирания / записи:

- Flash память - минимум 100000 циклов

- PLD - минимум 1000 циклов

- Сохранность данных: минимум 15 лет (для основной и вторичной Flash памяти, PLD и битов конфигурации)

Сигналами JTAG на порте C весь модуль PSD может быть запрограммирован или очищен без задействования MCU. Такая возможность очень удобна на этапе разработки и, кроме того, позволяет программировать законченное устройство (систему) на последнем этапе производства, что исключает воздействие температуры пайки на записанные в память данные. Кроме того, основная Flash память может быть внутрисистемно запрограммирована и путем выполнения микроконтроллером алгоритма программирования, записанного во вторичную Flash память или SRAM, что позволяет модифицировать код программы в условиях эксплуатации, используя любой из возможных каналов связи.

Вторичная память тоже может быть запрограммирована тем же самым способом с выполнением алгоритма программирования из основной Flash памяти. PLD или другие конфигурируемые блоки модуля PSD могут быть запрограммированы через JTAG порт или программатором.

Отметим, что модуль PSD приборов серии mPSD325X практически аналогичен прибору PSD серии PSD813F2, описанному в части 2 статьи, опубликованной в журнале Компоненты и технологии, №4`2003.

Крылов Е. И.

|